Test Languages:WAVES

WAVES

WAVES stands for Waveform and Vector Exchange Specification. It is a standard for defining input vectors, collecting the outputs of a design, and comparing the stored results with the received outputs from the CUT. WAVES includes a number of standard libraries developed in the VHDL language. In these libraries, several useful concepts and functions, which help a testbench developer, have been implemented.

Only the sequential subset of VHDL is used in WAVES. Therefore, this standard is more similar to a programming language, like the C-language, than an HDL. This standard has been standardized under IEEE 1029.1-1998 standard. There are two levels defined for WAVES specification: WAVES level 1 and WAVES level 2. WAVES level 1 includes the basic utilities and definitions for testbench development, while in WAVES level 2 more complex constructs are utilized for testbench development.

To test a design with WAVES, one should develop a testbench with the utility functions in WAVES standard libraries. This testbench has several parts including one for test vector reading and applying, one for storing the expected results, and another part for analyzing the outputs (comparing the expected results with the CUT outputs). There are also several tools developed for automatic generation of the necessary files from the description of the CUT. Figure 94.1 shows the flow of using WAVES in testing a design. Note that the testbench generated using WAVES can be used by both simulators and hardware testers.

In the following sections, the basic definitions of WAVES will be described. Then, the functions in the WAVES built-in libraries and the accepted formats for waveforms in WAVES will be discussed. Finally, the WAVES test set will be discussed using a simple example. For further study on WAVES, the reader is encouraged to refer to Refs. [1,2].

Basic Definitions

In this section, we will describe a few expressions and data structures used in the WAVES standard.

Logic Values

The input and output values used in WAVES are similar to the STD-1164 standard. There are two packages defined for logic values in WAVES. One package is WAVES_1164_pin_codes that defines input/output values as a STRING-type constant named pin_codes. In the other package (WAVES_1164_logic_value) an enumeration type named logic_value is defined for the input/output values. The values used in the WAVES_1164_pin_codes package are X, 0, 1, Z, W, L, H, and -. The “-” sign is for don’t care. The other values are interpreted as in the STD-1164 standard.

In the WAVES_1164_logic_value package, the values used in the enumeration type are dont_care, sense_x, sense_0, sense_1, sense_z, sense_w, sense_l, sense_h, drive_x, drive_0, drive_1, drive_z, drive_w, drive_l, and drive_h. The default value of variables of this type is dont_care, since this is the first member in this enumeration. The sense group in this type is used to show output values, while the drive group is used for the input values.

A difference between STD-1164 and pin_codes or logic_value types is the U value. U, which is the default type in STD-1164, means un-initialized. Initialization is only used in simulations, and not in real designs. Therefore, this type is omitted in WAVES. It is assumed that every signal in a design has a dont_care initial value in WAVES.

Slice

A slice or time slice is simply the tester cycle. This cycle can be interpreted as the period in which a test vector is applied to the CUT.

Frame

The list of transitions on a signal, which occurs during a slice, is called a frame. The set of frames for all possible patterns which can be applied on a signal is called a frame-set. Collectively, all inputs and outputs of a CUT generate a frame-set array.

t0, t1, and t2

Symbols t0, t1, and t2 represent predefined time markers. t0 represents the time in which a test cycle begins. t1 shows the time of leading-edge transition of a signal while t2 represents the time of trailing- edge transition of a signal. These definitions are used in waveform specification functions and procedures.

WAVES Built-in Libraries

WAVES built-in libraries used in upper-level packages are waves_standard, waves_interface, waves_port, and waves_object. Instead of discussing these libraries, we will show the usage of libraries that are more at the front-end of user interfaces.

Waveform Formats

To test and verify a CUT, a number of predefined test vectors must be applied to the circuit at specified times, and the responses from the CUT must be compared with the expected responses. To perform these operations, we have to define a format for input and output waveforms. These waveforms must carry test vector and output data. They must also have information about their timing (transition points) and their format (shape). There are several predefined waveform formats and timings (frames) that are implemented in the WAVES_1164_FRAMES package.

Predefined waveform formats are categorized into two main groups. One group is suitable for defining input (drive) waveforms and the other is for comparing output waveforms. The first category includes nonreturn, return high, return low, pulse high, pulse high skew, pulse low, pulse low skew, and surround by complement formats. In the second category, window and window skew, which are a span of time, are defined. Comparing the output to the expected output is done in this specified span of time.

As stated above, these formats are implemented as functions in the WAVES-1164_FRAMES package. This package uses functions and types defined in the WAVES standard packages to develop its functions. The waveform frame formats are described below.

Non-Return

As shown in Figure 94.2, if a signal has a transition in t1 and it holds this value until the next t1 (the leading edge at next t0), it has nonreturn frame format. It is important to note that in this and other figures related to frame formats Logic level 1 and Logic level 2 are two general logic values that only show a transition occurrence on a signal. For example, in Figure 94.2 Logic level 1 is not necessarily higher than Logic level 2. In the following figures, logic levels (high or low) are explicitly stated if necessary. In such cases, we show the logic levels with high and low labels.

Return High

In the return high frame format demonstrated in Figure 94.3, a signal has its data during a time interval between t1 and t2 (in one cycle) and it is held high between t2 and the next t1.

Return Low

The return low frame format is similar to return high format. They differ in logic value between t2 and the next t1. In this frame format, the signal value must be held low during t2 to the next t1. Figure 94.4 shows this frame format.

Pulse High

The pulse high format is a fixed frame format that is useful for signals like clocks in a design. The signal is held high between t1 and t2 (in one cycle) and becomes low until the next t1. Figure 94.5 demonstrates this frame format.

Pulse High Skew

The pulse high skew format is similar to the pulse high frame format except that in this format the signal must be held high between t1 in one cycle and t2 in its next cycle. This frame format is shown in Figure 94.6.

Pulse Low and Pulse Low Skew

The two frame formats, pulse low and pulse low skew, are similar to pulse high and pulse high skew (Figure 94.5 and Figure 94.6), respectively. Their difference is in their logic values. In these two formats the signal logic value must be held low between t1 and t2, and high otherwise.

Surround by Complement

In the surround by complement frame format, a signal has its data between t1 and t2 (in the same cycle) and the complement of that data between t0 to t1 duration and t2 to the next t0 duration. Figure 94.7 shows an example of a surround by complement frame format. This figure indicates that the signal is high in a cycle and low in the next cycle.

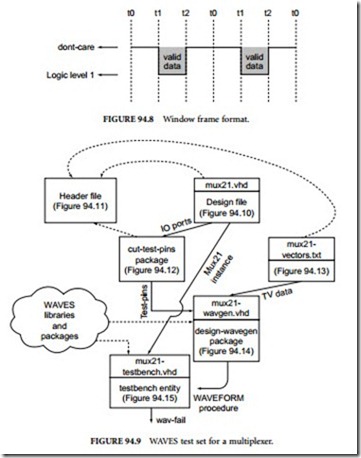

Window

A window is a time duration in which an output signal must have a specified value. It begins at t1 and ends at t2 (in the same cycle). For a correct comparison, the signal is set to dont_care in time durations t0 to t1 and t2 to next t0. Figure 94.8 shows an example of a window.

Window Skew

The window skew frame format is similar to a window, except that the output data is valid between t1 in a cycle and t2 in the next cycle.

All the above frame formats are implemented by functions with proper names in the WAVES_1164_FRAMES package (e.g., window_skew function for window skew frame format, etc.). When called with proper values of t0, t1, and t2, they return a frame-set which has all the possible waveforms for all logic values. The testbench developer uses a returned frame-set to look up the proper waveform for a given logic value.

An Example: WAVES Testbench for a Multiplexer

To verify and test a design with WAVES, a test set must be defined. As shown in Figure 94.9, this test set includes several files that all together apply test vectors to a design, measure the outputs, and compare the outputs with the expected results. These files include:

• A WAVES header file containing information about the author, revision level, files dependencies, external files, waveform generator procedure, etc.

• A VHDL package including an enumeration-type definition for test pins. Enumeration elements of this type are names of input and output parts of the CUT.

• An input pattern file.

• A testbench file.

• A process for conversions between binary test data waveform formats.

• Standard and upper-level 1164 packages and libraries.

The above test set can either be generated manually or automatically in part or as a whole. There are several automatic testbench generator tools that use the design file as input and generate the header file (or at least its structure) and a test pin file.

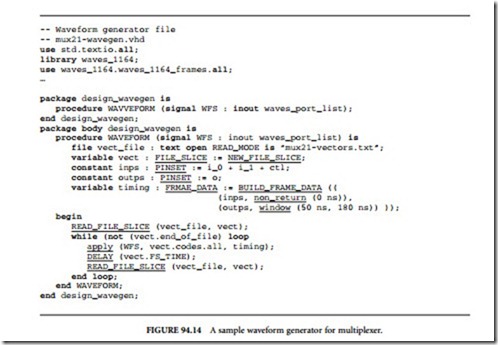

In this section, we use a 2-to-1 one-bit multiplexer as our example CUT. We will show various parts of WAVES test set (files indicated in Figure 94.9) that are needed for this example. Figure 94.10 shows the VHDL code for the multiplexer example.

The header file for this example is shown in Figure 94.11. This file contains all test set information.

The necessary test pin file for the multiplexer example is shown in Figure 94.12. Note in this file that test-pins type is defined to include inputs and outputs of the multiplexer of Figure 94.10.

A test data file for our example test set is shown in Figure 94.13. This file shows input data (ordered according to enumeration elements of test-pins), expected data, and time increments at which data is

used. As shown, data and timing are separated by a colon, and data slices are separated by a semicolon. The % sign in this figure marks a comment line. There are other formats for input data and timings that can be found in the IEEE WAVES document [1].

Another part of the multiplexer test set, shown in Figure 94.14, is a waveform generator file that includes a package containing the WAVEFORM procedure. This procedure opens the test vector file of Figure 94.13, reads input vectors and responses from this file, applies test data to the WFS port of the procedure, and reads the next slice after the given time increment (e.g., 200 ns in our example). In this procedure, we specify nonreturn frame format for the three inputs and the output. For each slide of data we use 150 and 180 ns for t1 and t2, respectively. The testbench calls WAVEFORM procedure in its waveform-generation part. The underlined phrases show that phrase is defined in WAVES libraries.

The above files and packages are used in the testbench of the multiplexer example shown in Figure 94.15. Similar to Figure 94.14, the underlined phrases in Figure 94.15 are implemented in WAVES libraries. For reading data, this testbench uses the WAVEFORM procedure of Figure 94.14. Instantiation of the CUT also takes place in this testbench. The last process in this testbench compares obtained and expected test data.

WAVES Level 2

As stated at the beginning of this chapter, there are two levels defined for the WAVES standard. The above discussions applied to both WAVES level 1 and level 2. In WAVES level 2, the WAVES user is allowed to build testbenches using more complex data structures and features of VHDL.

Constructs supported in WAVES level 2 include:

• Floating-point types

• Composite data types like arrays of records

• Access types

• Type castings and conversions

• Subtypes

• Variable assignments: in WAVES level 1, variables can only be assigned in the initialization phase

• Complex file operations: using predefined TEXTIO procedures, such as read and write, is allowed in WAVES level 2

Although there are VHDL features added to WAVES level 2, there are still several constructs that are not supported. These constructs include:

• Components and configuration specifications

• Signal declarations and assignments

• Wait statements

• Aliases, attributes, file, and physical types

Our Coverage of WAVES

In this section a library that is based on the VHDL language for generating efficient testbenches was discussed. Testbenches developed as such can be used for simulation-based verification of a design or they can be used by testers to perform a manufacturing test. The next section discusses another test language for hardware designs.

Comments

Post a Comment