LAYOUT DESIGN:IMPLEMENTING THE DESIGN

IMPLEMENTING THE DESIGN

Let us now put all of the knowledge we have learned so far to work. At this point we have all of the fundamental knowledge to complete a basic layout design.

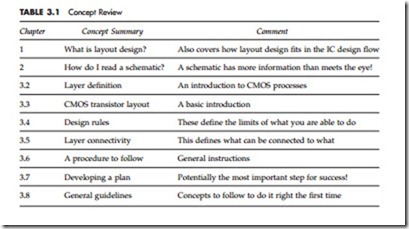

First, let’s review the key concepts presented so far (Table 3.1). If you have mastered these fundamental concepts, you should be able to tackle almost any layout task.

We have learned that before we start any layout design, we must make a plan. Before we go ahead and execute this plan, it is always important to anticipate what the next steps are and keep these in mind as we implement our design. In this way we minimize or eliminate the amount of rework caused by our own ignorance.

Component placement (Step 2.1 from Figure 3.32) based on the floorplan is another area where we will always achieve a good return on the effort invested in doing a proper placement of components. The ability for the design to be completely routed is usually limited by the placement of components. These compo- nents can be other transistors, tub contacts, power supply lines, or interface

locations for signals, in addition to instantiated components. Any extra effort in the placement stage will be rewarded in the long run by having an easily routable design.

It is at this stage that signal lines or interfaces should be labeled and identified to avoid connection errors. This would include power, signal, feed-through, and other polygons.

Step 2.1 can be considered to be an initial placement to validate that the floorplan is feasible. In Step 2.2 we start to consider finer details, where we have to deal with special design requirements such as the critical path signals, substrate contacts, layout symmetry, specific requirements for latch-up protection, or noise immunity. Detailed placement will occur in this step as well as the routing of important or difficult signals. Power supplies and clock signals fall into this category. In addition, extra space for components and routing should be allocated in anticipation of new design requirements after the layout has been started or completed.

With a good floorplan and final placement of components, Step 2.3 becomes very easy. Without the former, completing interconnect routing while respecting special design requirements is usually difficult and time consuming. Remember that the floorplan should have considered the routing layers, the direction of routing, and the space for routing all signals, so by this time completing the routing should be fairly straightforward.

Let’s now examine issues related to specific types of layout designs.

Cell Layout

The leaf or logic cell is in general a layout that is drawn from a transistor-based schematic; therefore, the majority of components to be used in this type of design would be polygons, transistors, contacts, and signal pins. “Polygon pushing” is the layout design style used here, as we are implementing circuitry at the lowest level of abstraction and we need detailed knowledge of the entire set of layers and layout design rules. Formally, this is known as a “full custom” design style.

The key concepts to be addressed at this level of layout include the following:

• Detailed knowledge of the entire set of layers and layout design rules.

• The size of the design, estimated from the number of transistors in the design and the layout design rules.

• Attention to transistor-level placement and interconnect to implement logic gates.

• Careful floorplanning and architecture definition to minimize area and maximize performance. These leaf cells are potentially used thousands of times, so the extra effort in achieving area savings for each cell is justly rewarded in the finished chip.

• Careful design of the power supply implementation. This also includes consideration of substrate and tub contacts. If this is done well, the power supply routing and bulk connection requirements of an entire block or chip can be met by building these requirements into the design of the leaf cells.

• Attention to the design of the interface to other cells. As mentioned previously, these leaf cells may be used many, many times, and area savings can

be achieved by minimizing the overhead required to place two leaf cells adjacent to each other. Ideally, leaf cells should be designed to abut directly to all possible cells that may be placed adjacent to them.

Block Layout

The difference between a cell and a block is open to interpretation, but in general a cell is referred to as a block when it incorporates circuitry of medium complex- ity and functionality and is mainly composed of instantiated cells. Blocks are larger and more complex than cells and are implemented by designers with more experience than those who can design cells. We consider this design style to be a “semi-custom” design style, as it combines cell-based design with full custom design. The layout flow described in Figure 3.32 still applies.

The important factors to keep in mind for block level design are as follows:

• The size of the design is estimated from the number of cells in the design and the number of external and internally routed signals.

• It is most common in blocks to have a significant amount of space allocated for spare components and signals as well as signals that may simply pass through the block. These signals are referred to as feed-through signals.

• Some blocks will have functionally different components such as a mix of digital and analog cells. In this case there may be special considerations for the different circuit requirements such as latch-up and noise immunity.

In general, when the layout designer has all the above information, it is time for placement of the previously made cells, transistors (if any), and interconnect routing.

In general, blocks are defined based on the circuit functionality and the layout style. Examples that are common might be row cells, standard cells, data- path or register files, I/O (input/output) ring, analog blocks, and memory blocks.

Chip Layout

Implementation of the full chip layout is conceptually identical to that of a large block in that the steps from layout planning through to auditing remain the same.

Full chip layout designs will incorporate blocks and cells of diverse types, so detailed knowledge of all layout design styles is required to maximize the chance of success.

Aspects that must be addressed at the chip level and generally nowhere else include the following:

• Design partitioning of very large and diverse blocks. Defining the many interfaces of a complex chip is a complicated task.

• Defining and planning the interface to the outside world. This involves knowledge about pad and I/O circuitry and the intricacies associated with them.

• Planning and implementing critical signals that are routed over the entire chip. This would include global power supplies and clock signals.

• Floorplanning techniques and maintenance are of paramount importance here. At the full chip level the floorplan is critical as a communication tool as well as a layout implementation tool.

• Estimating the chip size is a significant task in itself. Estimates from previous designs and previous experience should play a role in completing this task. Compare the process parameters of the current project to previous ones. This is one area in which expertise in floorplanning tools can really help.

• In the role of a layout leader responsible for a full chip layout, there is also the requirement to define layout methodologies, task allocation, and scheduling for the entire team. Also, an understanding of the suite of layout design and layout verification tools is important in ensuring that the team performs efficiently.

Overall, it is the complexity of the task of the full chip layout that makes it one of the most challenging and interesting roles in layout design.

Comments

Post a Comment