ADVANCED TECHNIQUES FOR SPECIALIZED BUILDING-BLOCK LAYOUT DESIGN:STANDARD CELL LIBRARIES

STANDARD CELL LIBRARIES

A library of logic cells is the set of building blocks for the ASIC design flow dis- cussed in Chapter 4. The library is typically called a “standard cell” library because of its common interface implementation and regular structure.

The library provides the functional building blocks used for synthesis and a layout representation of the cells for place-and-route. It is very important to note that the process of HDL synthesis limits the choice of logic cells to those that are found in the library provided. This guarantees that a physical or layout representation of the cells exists when the design is implemented using place- and-route tools.

A Brief History of Standard Cells

One way to understand the required layout characteristics of standard cells is to understand their history and the reasons behind their development. Once the concepts and methodologies behind this design process are understood, it is easier to fully appreciate the layout requirements for the cells themselves.

Why were libraries developed?

• Independent blocks became too big and complex for a full-custom design, so there was a need to speed up the circuit and layout design processes.

• There was a shortage of specialized personnel capable of hand-crafting complex full-custom designed blocks; automation alleviated this problem.

• Advances in the typical manufacturing process included increasing the number of routing layers from one to two or three metal layers. This added further complexity to the full-custom layout design process for optimal results.

• Even in a full-custom design flow, the placement of more than 20 cells is easier when the building-block cells are implemented with predefined standards. The standardization of cell interfaces is a concept that is implemented in a library.

The solution was to simplify the circuit and layout design of large digital circuits by using predefined and characterized “building blocks” (cells).

Before circuit synthesis tools were available, at first the idea was to develop predefined simple logic circuits. Examples would be inverters, NANDs, NORs, and flip-flops, to name a few. These would be designed and analyzed by an expert and then released to the project for general use. Everybody would be able to use these cells as building blocks for their circuits.

In order for a particular logic cell to be useful in different situations, the library was expanded to include each logic cell in a variety of sizes. Initially, the various sizes were decided haphazardly by individual designers.

A further refinement was to define the different sizes of each logic cell in the library so that the design can be more easily correct by construction. This is accomplished by following fanout guidelines in the case of amplifying a signal to drive bigger and bigger loads. For example, if the minimum size inverter is specified to be P2.5/N1.25, then the different inverter sizes in the library would be multi- ples of this size. A 2¥ inverter or INVx2 would have a size of P5/N2.5, INVx4 P10/5, etc.

Standardizing the sizes ensures that nobody will try to use weird numbers such as P8/N4 or P6/N3 in the circuit design phase, and maximum sharing of components is achieved.

When the synthesis flow was developed, the circuit designer actually didn’t see the layout cells, so the need for standardization became even greater. As we mentioned previously, the synthesis tools automatically choose the best cell for the job; therefore, if a larger selection of cells is available, the synthesis tool has a better chance of optimizing the circuit.

Another factor that influenced the development of library cells was the impact of the first automatic place-and-route tools. The first automatic routers that came out started to change the way designers implemented full-custom connectivity, because the routing tools worked best with cells built in a certain way. Cell design was (and is) heavily influenced by the restrictions of the automatic tools.

Today the standard cell is the foundation of ASIC design. There are companies whose sole business is the design and migration of libraries into different manufacturing processes. Various EDA vendors provide circuit and physical design tools specifically for libraries as well.

ASIC design notwithstanding, the standard cell design methodology is also widely used to implement the “random logic” of a full-custom design. Initially, a circuit is partitioned into several smaller blocks, each of which is equivalent to some predefined function. Within each logic block, cells are implemented from a

set of library cells. In general, the library is much smaller than a commercial ASIC library, but the methodology is the same.

Standard Cell Characteristics

A simple NAND gate is shown in Figure 5.1. A standard cell representation of the gate is shown. As we have discussed, an ASIC layout design is implemented at the cell or gate level, and detailed knowledge of the contents of the gate is not required.

In this section we will discuss the design of the cell itself. The goal is to give an understanding of the standard cell design so that it is compatible with an ASIC design flow. There are many issues to consider. First and foremost, however, is that the library of cells be compatible with the specific limitations or features of the manufacturing process to be used.

Typically, the design or architecture of the standard cells should be chosen based on the number of routing layers available in the target manufacturing technology. In certain special cases the design of the cells will depend on the characteristics of the available metal layers.

The following is a list of characteristics that are common to all standard cell libraries.

Characteristics related to the circuit design are as follows:

• The functionality and the electrical characteristics of each cell is tested, analyzed, and specified. In general, a test chip is manufactured and the performance of the each cell is analyzed from silicon. In some cases, only a process characterization step is completed to generate simulation models of the transistor characteristics, and library characterization tools use these models to create the simulation views of each cell.

• Multiple drive strengths for each cell type are created. In addition, the different drive strengths are multiples of a base or minimum size.

The following characteristics are related to the basic shape of the cells:

• During the layout design of the cells, the cells are built using a predefined template that will ensure that all the requirements are met. The template includes the height of the cell, the placement of wells, N transistors, and P transistors, and guidelines to follow so that the cell can be flipped vertically or horizontally and can be placed beside all other cells without creating errors such as DRC violations.

• Cells are rectangular.

• Cells for specific rows or chip areas are all the same height—a library may contain multiple sets of cells. For example, different cells will be used for logic, datapath, and I/O areas.

• Every cell length is rounded up to a multiple of a coarse grid. This grid is determined by either of the following:

A specific design rule (such as the minimum well width)

A desire to make placement easier and faster (using a coarse grid reduces the number of possible placement coordinates, thus accelerating the placement process)

• The power supply lines have a predefined width and position for the entire library—the width of the supply over the cell length is always consistent.

The following characteristics are related to the interface of the cells:

• All the input and output ports have a predefined type, layer, position, size, and interface points. These characteristics are determined based on the placer and/or router to be used to implement the design. The ports are targets for the router and should be optimized with the router in mind for best results.

An example of this would be that routing can be made faster and easier by using a signal pitch that is defined on a coarse grid. Routing tools will use fewer computing resources if a coarse grid is used because the arithmetic required of the tool is simplified.

• The interface of the cells can be designed to share certain connections. Examples would be source connections of transistors that are connected to power supplies. Alternatively, common substrate and tub contacts can be shared between cells.

• A rectangular outline and a set of obstructions for each routing layer are also characteristics of each cell. Obstructions can be defined separately for each routing layer, or the entire outline of the cell can be used as an obstruction. Obstructions can have any shape. They are not restricted to rectangles, but they have to be recognized by the routing tool.

• All nonshared polygons have to be spaced from the boundary of the cell by a value equal to one-half of the layer spacing design rule. This ensures that abutting cells will be correct by construction.

Other things to note about cell libraries:

• There are cells without any transistors, called feed-through or filler cells, that can be added between cells to allow vertical connectivity when there are no more routing resources over the cell.

• In the case of I/O cells, there are specially shaped cells for the corners of the chip where two rows of cells meet.

A typical standard cell library consists of hundreds of cells. Advanced libraries consist of more than 1,000 cells. There are cell libraries specially designed and developed for low power consumption, high speed, very good porosity, etc.

Standard Cell Architectures

As we stated in the previous section, the design and architecture of a standard cell is dependent on the number of routing layers that are available in the manufacturing technology. Let’s investigate why. An example of a standard cell is shown in Figure 5.2.

Note that only one layer is used to make most internal connections to the transistors within the cell. This version of a standard cell is compatible with the early versions of channel routers. These routers could only make connection to cell pins that were placed on the boundary of the cell.

As you can see in Figure 5.2 the connections to the second layer of metal is made to the cell to ports only on the top and bottom sides.

The design shown in Figure 5.3 consists of two rows and a routing channel in between. Note the feed-throughs in the design. They are empty cells that are

there to accommodate vertical tracks that connect signals located in different routing channels.

In a process with only two routing layers, feed-throughs are the only way to add vertical routing tracks. In this case the routing is done in two steps. First, enough feed-throughs are assigned to implement the required number of vertical running signals. The completion of the rest of the routing follows feed-through placement.

When a different design is done that accommodates vias in the middle of the cell, then ports can be placed there and over-the-cell routing is possible. Refer to Figure 5.3 for a clear example. In this case vertical routing tracks are possible over the cells and the use of feed-throughs is reduced in the final design.

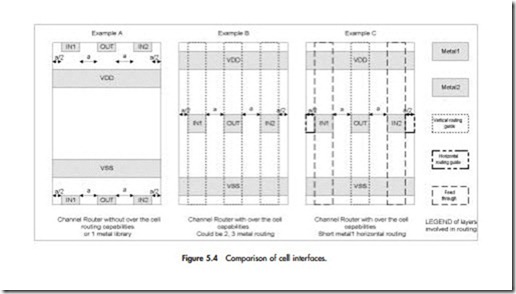

Figure 5.4 compares the two cell architectures and the differences in the ports and interfaces to the designs.

Note that in Example A, the ports to the design have to be accessible on both the top and bottom sides of the design. This is to ensure that routing channels are used most efficiently and it minimizes the use of separate feed-throughs. The over- head of routing these ports within the cell to two sides of the cell is significant, adding parasitic loading to the signals and reducing the overall porosity of the final design. Examples B and C do not suffer from this overhead, and a cell equivalent to Example A may be smaller overall.

Example C in Figure 5.4 shows an advantage of over-the-cell routing and clever interface design. In this case, the connections to the IN1 and IN2 ports may be extremely short if the cell that is connected to it is placed directly adjacent to the one shown. In this case, space is not consumed in any routing channel.

Figure 5.5 compares two routed designs with and without over-the-cell routing. In both cases there are only two layers of metal available for routing, but the difference is whether or not over-the-cell routing is possible.

In the top picture, we can observe that the channel used for routing can only be the empty space between cell boundaries. In the second example this restriction is not as acute. The area of the second design is significantly smaller and for large designs the difference is amplified. The main reasons for the smaller area in the case of over-the-cell routing can be summarized as follows:

• The router can route horizontally between adjacent out–in port connections.

This is a major source of area savings, as the routing channels between cells are reduced by this effect alone.

• The available channel size includes the cell area and therefore is more efficient.

• Porosity is much greater because of the metal1 horizontal connections between adjacent cells, because of the reduced cell size due to the elimination of routing port signals between top and bottom sides, and finally because of the elimination of feed-throughs.

In a three-metal-layer process, almost all the channels can be removed and all routing can be completed over the cells.

More Standard Cell Concepts

We have mentioned the term “porosity” of a design. The porosity of a design can be used as a metric of quality and/or efficiency of a design. Porosity as it relates to layout design is defined as the ratio of the total available routing area to the total cell area. Cell pins are not included as routing area.

For example, in the case where many pure routing channels are used, the porosity is low. Ideally, we want to increase the porosity of a design by eliminating any channels and have only the logic cells that are needed to implement the design.

We may need to trade off porosity within a library to ensure that we can complete the design in a reasonable amount of time and take advantage of any features of the place-and-route tools. At the same time we need to avoid limitations that these tools might have. It is useful to read the manuals for the place- and-route tool to be used before designing the library of cells.

Among other things, we have already mentioned that a coarse routing and cell size grid is useful for reducing the compute resources of the place- and-route tools. This and other points to note when designing standard cells are as follows:

• The choice of routing grid is important. There are three types of grid used today: line to line, line to via, and via to via. Figure 5.6 shows examples of the three cases and how they may affect standard cell design.

The line-to-line pitch suffers from the fact that a lot of signal jogging is required whenever a via is used. The cell size is the smallest, but routability suffers. Also, the execution time for the routing engine to complete the job will be much longer.

Similarly, in the case of via-to-line pitch, signal jogging will occur whenever two vias happen to be placed on adjacent lines. Trying to avoid this case is an overhead that may negate the area benefit of the reduced signal pitch.

In the case of via-to-via pitch, the porosity of the design is maximized and the routing is more straightforward.

• The standard cell height and maximum cell length for the library must be determined based on the tools to be used, the purpose of the library, porosity, and number of routing layers.

For example, in the case where metal1 is the layer used internally to the cells, there is a rule of thumb that says, “The length of the longest cell

has to be no bigger than six times the cell height.” In the case where cells will be longer, the cell height should be dramatically increased (perhaps doubled). The reason for this is that the placement tools can work much more easily with a reasonable height-to-length ratio. A long cell is much more likely to have internal metal2 jumpers, so the porosity is reduced for routing.

• Power supply issues for the entire block must be addressed before the place- and-route takes place. Strapping and connecting the power supplies is always attacked first when implementing a standard cell design. The fol- lowing issues should be considered:

Connectivity between standard cells

Tracks routed internally to the standard cells

Electromigration applied to track width and number of vias

Resistance

• Since the place-and-route tools are only concerned with the placement and connectivity to standard cells it is useful to consider the design of the cell abstract. The cell abstract is not a physical part of the design, but is used only by the place-and-route tool. The abstract consists of the following: Cell boundary

Location and shape of target pins Routing obstructions

Routing obstructions or “keep outs” are areas within a cell that are unavailable for routing in the assigned layer. For example, very little area within most standard cells is available for metal1 routing because there is a lot of metal1 used for the local interconnections.

If the router is free to use metal1 in trying to connect cells, it has to know where it can and cannot place signal tracks. Obstructions within the cells give the router this information in the form of shapes on the given layer.

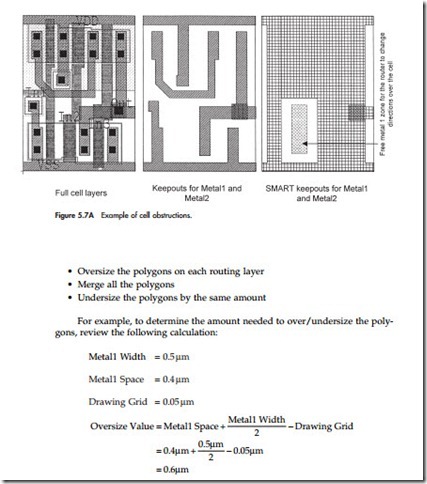

Figure 5.7A shows an example of a standard cell and the areas of metal1 use. One approach to defining the obstruction areas would be to replicate all metal1 shapes.

Even for small blocks (500 cells) there is a strong dependence between the compute time of a router and the way the obstructions are defined. The routing software algorithms needs to build a map of the routing porosity for every layer, so the more complicated the shapes are in the keepout layers, the bigger the files. With complex polygons the computational requirements become longer and more complicated and the routing time starts to grow exponentially. So let’s see how we can help the tool to run faster and more efficiently, using fewer computer resources. Refer to Figure 5.7A for an example.

In Figure 5.7A you can easily see that the smart keepout is only one polygon on metal1 and that it has a minimal number of coordinates. Not only is the obstruction concisely defined, but there is an open space for the router to use in case there is a need to put down vias for routing.

To automatically obtain a shape like the one on the right we can use a simple macro that will do the following:

Figure 5.7B shows a graphical implementation of the above steps.

The intent is to obtain one single shape that will cover all the small polygons. This shape will include the places where the distance between two of them is smaller than the possibility of routing another nonrelated line. Doing so for each cell in the library, for each routing layer, we can significantly reduce the place and-route time.

Gate Arrays

This design style is a different approach to standard cell design.

Unlike standard cell design, where all layers are different from one cell to another, every gate array cell within one particular library has an identical arrangement of a base set of layers.

Typically, this base set of layers includes only the layers necessary for the formation of transistors; therefore, the list of base layers would include wells, active regions, implant layers, gate polysilicon, and nothing more.

Upon this base set of layers, individual “standard cell” functionality is obtained by patterning the interconnection of the transistors into different configurations. Refer to Figure 5.8 for a pictorial explanation of how cells are defined. Typically, the interconnection layers are the first one or two layers of metal. These defining layers are collectively known as the “shades” of the cell and are the only layers that are different from cell to cell.

The term gate array comes from the way in which an entire design is implemented. In a gate array design, an entire wafer can be prefabricated with an array of identically patterned transistors or groupings of transistors called base cells. Logical definition of the standard cells and of the connections between them uses only the shades of the required cells and the free routing layers.

Comments

Post a Comment