LAYOUT CONSIDERATIONS DUE TO PROCESS CONSTRAINTS:LATCH-UP.

LATCH-UP

Conceptually, latch-up refers to the state of an IC when it is made inoperable by a parasitic shorting of VDD to VSS. Depending on the severity of the latch-up condition, the IC may be irreversibly damaged, or it may recover only after a complete power shutdown.

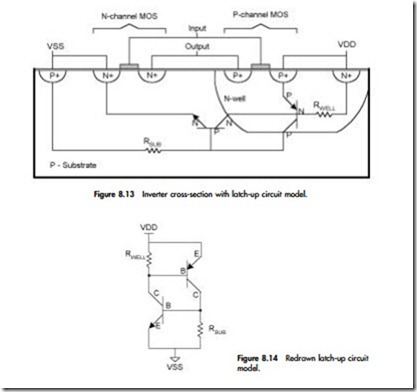

Let us try to understand, in a brief way, how latch-up comes about. Figure 8.13 shows the equivalent circuit model of the parasitic devices we refer to within a simple CMOS inverter. Transmission gates are a another risky source of latch-up, especially if the source or drain of the transmission gate is connected to VDD or VSS.

Redrawing the schematic of Figure 8.13 into a more readable format, we end up with the drawing shown in Figure 8.14. Very simply, latch-up occurs if either of the two bipolar transistors is turned on. If this happens, there is a positive feedback loop in that when one transistor turns on, the resulting current flow encour-ages the other transistor to turn on as well. Positive feedback occurs once again as the second transistor’s current flow strengthens the first transistor’s drive and the vicious cycle feeds upon itself. Under normal conditions, latch-up is not likely to occur, so how do these transistors become activated? First, let’s very briefly discuss how bipolar transistors work.

Similar to MOS transistors, bipolar transistors are activated when there is a voltage difference between the base (labeled B) and the emitter (labeled E). NPN bipolar transistors require a positive VBE, whereas PNP transistors require a neg-

ative VBE. We should recognize similar functionality of transistors to that of the voltage requirements in activating NMOS and PMOS transistors.

What triggers latch-up if under normal conditions these parasitic bipolar transistors are off? The most common trigger for latch-up is undesired or extreme currents injected into the Chip through the power supplies VDD or VSS. These nodes are connected directly to the outside world and thus are constantly exposed to uncertain voltage and current levels.

Let’s go back to analyzing the schematic shown in Figure 8.14. As an example, let us imagine an abnormal current being injected into VDD from the outside world. This current results in a voltage drop across RWELL by Ohm’s law—and voilè, we get our negative VBE for the PNP transistor, and it turns on. The current produced by the PNP transistor causes another voltage drop across RSUB, therefore turning on the NPN. The NPN transistor current sustains the voltage drop across RWELL, keeping the PNP transistor on even if the external VDD current has disappeared. The PNP current in turn sustains the operation of the NPN, and this vicious circle is latch-up.

In summary, here are the very simple requirements for latch-up to occur that we have discussed:

• A large enough VBE generated (at least temporarily) to activate either bipolar transistor. This requires the combination of an abnormal current injected into the chip and parasitic resistance values large enough to generate this voltage difference by Ohm’s law.

• Parasitic bipolar transistors of sufficient current drive strength to sustain the required VBE to keep the bipolar transistors on.

Latch-up is a phenomenon that is well understood, as it has a long history in CMOS IC design. Many guidelines and design rules have been developed that inherently reduce the risk of latch-up and minimize the likelihood of meeting the requirements just listed.

A straightforward strategy to reduce the likelihood of latch-up would be to reduce the parasitic resistances across the base-emitter nodes and therefore increase the current requirement to trigger latch-up. If this is done properly, the trigger current for latch-up may be large enough that it is physically impossible.

In general, these techniques also weaken the strength of the bipolar transistors by breaking up the chip area into fragmented areas and therefore reduce the effective size of the various bipolar transistors.

Layout methodologies that reduce susceptibility to latch-up include the following:

• Avoid routing power supply lines (especially to substrate or tub contacts) in resistive materials such as diffusion or polysilicon. Keep the power nodes in metal!

• Place substrate and tub contacts between transistors of different types. In addition minimize the distance between substrate contacts and transistors within a well and vice versa. For example, if PMOS transistors are within an N-WELL then place the P-type substrate contacts as close as is allowed to the PMOS transistors. Apply the same logic to the N-type tub contact spacing to NMOS transistors.

• Maximize the number of substrate and tub contacts.

• Minimize the spacing between substrate and tub contacts.

• Ensure an even coverage of substrate and tub contacts over the entire area.

• Use continuous strips or bands of substrate and tub contacts. This technique is formally known as guard banding, especially when the bands completely surround transistor areas.

• Group transistors of the same type together to avoid the overhead of having to protect against latch-up in many different areas.

• Place internal circuitry away from external pad areas.

• Be extra careful in considering latch-up conditions in areas where the substrate or well is not the same potential as the source nodes of the transistors.

In all cases, it is always best to develop formal numerical design rules that can be checked by the layout verification tools. Many of the methodologies just

listed are not easily converted to numerical checks, but we recommend at least the following: A design rule specifying a maximum distance between substrate or tub contacts.

In general this distance is about 40 to 50 mm, but as the gate length of transistors shrinks, this guideline should be reduced. This rule ensures an even coverage of a given area with bulk connections, and there will be consistent voltage all over the area.

There are two basic ways of checking this distance: from active to active or from contact to contact. Figure 8.15 shows both ways of measuring these distances. Both styles are correct depending on the number used to check the distance between them.

The second rule is area coverage of each contact based on substrate or N- well resistance. Each of these actives has substrate coverage to prevent latch-up of about half the minimum distance between them. So if the minimum distance is 50 mm, then the coverage is 25 mm.

Note from Figure 8.16 that while the layout conforms to the rule just given, the distance between the four contacts leaves a small island of transistor area that is not protected. The shaded area from each contact (gray) with the dark lines is the coverage radius of the four tub contacts. The noncovered area is the middle white region.

For a layout to be completely verified, both of these rules need to be satisfied. Big transistors or very high-speed circuits that are switching fast and continuously can inject a lot of noise into the substrate by their size. Examples are clock generators or output buffers. It is advisable to use full guard rings for all tubs and substrate connection around the transistors.

In layout, these guard rings are divided in two basic kinds, hard and soft ties. The hard tie is a fully contacted ring of active that has continuous metal1 over it. Soft ties have a continuous ring of active, but the metal layer may be broken to accommodate signals passing into the guard ring.

Figure 8.17 illustrates the differences between hard and soft ties.

Comments

Post a Comment