System Verilog:Variable Declaration

Variable Declaration

In Verilog-95, all variables and nets should be declared in the module body enclosed by keywords module and endmodule. However, declarations outside the module body are allowed in System Verilog. Such a variable is visible in all modules compiled at the same time with .the file containing the variable. In

Figure 90.4, a 3-bit binary variable, called alu_func, is defined. To find the reference of a variable, the local variables in the scope are searched first. If the variable is not found, then it is searched outside the module. The alu_func in model m1 refers to the alu_func declared outside the module, while alu_func in module m2 refers to its alu_func input port

Net and Variable Assignment

In Verilog-95, a net type can be assigned from an output of a module or through a continuous assignment statement, while a variable of type reg can be assigned in procedural assignment statements. In System Verilog, these restrictions are removed from existing and new data types. This means that any variable of any type can be assigned by only one of the following ways:

• From any number of procedural blocks (i.e., initial and always block)

• From an output of a single module (or primitive)

• From a single continuous assignment statement

Figure 90.5 shows an example of variable assignment. In module m1, a variable of type reg, named y1, is assigned in a continuous assignment, which is a valid use of the reg-type in System Verilog. In contrast, a reg-type variable, named y2, is assigned in both continuous and procedural assignments in module m1, which is not valid (because of the mix of continuous and procedural assignment to a variable). In Figure 90.6, a variable of type logic, named y1, is assigned in two continuous assignments, which is

not a valid use of the logic type. In the same figure, a valid use of type logic is shown. Variable y2 of type logic is assigned in a procedural block.

Type Casting

System Verilog provides static (compile-time) and dynamic (run-time) type casting. There are three types of static casting used for casting a value to a specified data type, casting a value to a specified vector size, and casting a value to signed or unsigned. Dynamic casting is performed by using the $cast (des, src) system function which casts the src variable to the des variable.

Figure 90.7 shows several examples of type casting. In the first example, the value of 56.00 is cast to byte. The second example shows casting the value of a to a 16-bit vector size. The third example shows casting the value of b to a signed value and finally the last example, that consists of a declaration and a dynamic cast, shows casting the value of expression 2.0 ∗ b to the shortint data type.

User-Defined Data Type

System Verilog allows new data type definitions with the typedef keyword. The syntax of the typedef statement is:

typedef type name ;

where type is an existing data type and name is the new name for this type. Figure 90.8 shows an example of a user-defined type definition.

Enumerated Data Type

Enumerated data type is a set of user-defined names that specifies all the valid values that a variable of that type can obtain. Each user-defined symbol corresponds to an integer value one greater than the previous symbol. The value of the first symbol is 0.

Figure 90.9 shows an example of enumerated data type definition, which is used for state machine coding. Variable present_state can have the values of init, got1, got11, and got110. The integer values of init and got11 are 0 and 2, respectively.

The default integer value assigned to a symbol can be modified explicitly by assigning the desired value to the symbol. Figure 90.10 shows an example of legal code assignments to the enumerated symbols. This feature can be employed to specify a desired code assignment in state machine implementations. Figure 90.11 shows an example of a one-hot code assignment to the states of Figure 90.9. As shown in Figure 90.11, the lengths of the enumerated symbols are specified and matched with the assigned codes. Figure 90.11 also shows an illegal code assignment due to the violation of this rule.

Array Type

In Verilog-95, only one-dimensional array declarations of data type reg, integer, and time are allowed. System Verilog extends array declarations to allow multidimensional array declarations of any data type, and calls it unpacked array. The syntax of an unpacked array declaration is as follows:

<type> <name> <dimension 1> … <dimension n>;

Figure 90.12 shows several examples of unpacked array declarations. Variable a1 is a one-dimensional array of 16 elements of a 1-bit wire type. Variable a2 is declared as a one-dimensional array of 1024 elements of 8-bit reg vectors, and finally variable a3 is declared as a two-dimensional array of bytes.

An array element can be accessed using indexes. Figure 90.13 shows how to access the fifth element of array a2 and how to access the second row and the third column of array a3. As shown in this figure, you can assign 0, 1, Z, and X values to all bits of a vector using '0, '1, 'Z, and 'X, respectively. So the statement a2[4] = '0; sets all bits of the fifth element of the array a2, which is an 8-bit reg vector, to 0. Bit select and part select access to an array are allowed in System Verilog, and multiple select that selects multiple elements of an array is not allowed.

The C-like style can be employed to initialize an unpacked array. Figure 90.14 shows an example of initializing an unpacked array. This statement assigns values 0, 1, … to a4[0][0], a4[0][1], … elements

of a4, respectively. Unpacked array assignment is performed in the same manner (see Figure 90.14). System Verilog adds the default operator to fill all array elements with a specified value. As shown in Figure 90.14, statement a4 = {default: 5}; fills all elements of a4 with 5.

System Verilog also provides multidimensional vectors of the following types: bit, logic, reg, and net. This type of vectors is called packed arrays. Packed arrays are declared based on the following syntax:

<type> <dimension 1> … <dimension n> <name>;

Figure 90.15 shows an example of packed array declaration. Variable pa is declared as a two-dimensional packed array. As shown in Figure 90.16, we can consider pa as a vector with two elements, where each element is a 4-bit logic vector. System Verilog allows access to multiple elements, bit select, and part select of a packed array as illustrated in Figure 90.15. As shown in Figure 90.16, packed arrays can be assigned using simple assignment statements. Assignments to bit select, part select, and also to a slice of an array are allowed in System Verilog.

Structure Data Type

Structures can be defined in System Verilog using a C-like syntax. As in software languages, a structure is a collection of various elements that are not necessarily of the same type. Figure 90.17 shows an example of structure definition. The variable inst has four fields including opcode, rs, rt, and adr. An element of a variable of type structure can be accessed using the C-like “.” operator, for instance statement inst.adr = 'b0 is used to fill in the adr element of the inst variable with zeros.

A set of values enclosed in { } and separated by commas can be used to assign values to elements of a structure. As with unpacked arrays, all structure elements can be set by a default operator. Figure 90.18 shows two types of structure assignments.

Union Data Type

As in the C programming language, union in System Verilog is a memory location shared by two or more different variables. The union declaration is similar to structure declaration and the union elements can be accessed in the same way. Figure 90.19 shows an example of union declaration, mapping its two elements together. The elements are a 16-bit integer variable word, and a packed array called bytes. As described before, these two elements share memory locations (see Figure 90.20). In module test_union a 16-bit value is assigned to element word of the union and can then be accessed as two bytes through element bytes.

Operators

The increment and decrement operators (++ and – –) are added to System Verilog. The operator ++ (– –) adds (subtracts) 1 to (from) its operand. If the operator ++ (or – –) appears before the operand, the increment (or decrement) operation is performed before using the value of the operand. However, if these operators appear after the operand, the value of the operand is used before incrementing (or decrementing) it. These operators have a blocking behavior, which means that they block their following statements until they are completed. Figure 90.21 shows an example of increment and decrement operators used to describe a 4-bit up-down counter.

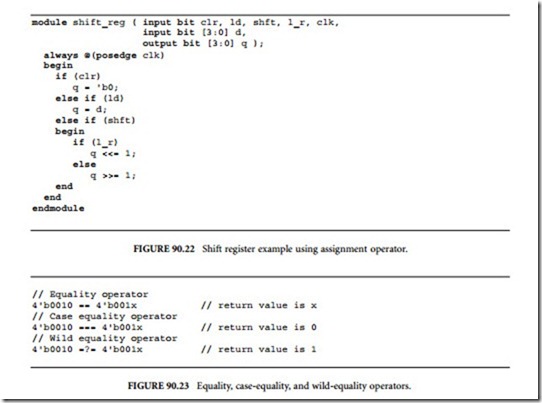

System Verilog also provides several C-like assignment operators including +=, –=, *=, /=, %=, &=, |=, ^=, <<=, >>=, <<<=, and >>>=. Assignment operators perform the specified operation on both left- and right-hand-side operands and then the result is assigned to the left-hand-side operand. The last two operators are used for arithmetic left and arithmetic right shift operators. Because of the blocking behavior of the assignment operators, special care is needed to be taken when using them. Consider a shift register with the truth table shown in Table 90.1. The module shift_reg, shown in Figure 90.22, describes the functionality of the shift register using a procedural always block. The assignment statement q <<= 1; means that the value of q is shifted 1 bit to the left and then the result is assigned to q.

System Verilog also adds two new equality operators called wild equality operator (=?=) and wild inequality operator (!?=). The X and Z value in a bit position in any operand are treated as a don’t-care bit and can be matched with any value. The wild-case equality operator returns 1, if the operands are equal, and returns 0 otherwise. To check the equality of the operands all X and Z values in any bit position are considered as don’t-cares and can be matched to all logic values (i.e., 0, 1, X, and Z). Figure 90.23 shows an example of using equality, case equality, and wild equality operators and illustrates their differences.

Comments

Post a Comment