LAYOUT DESIGN:PROCESS DESIGN RULES

PROCESS DESIGN RULES

Design rules are the rules that have to be respected when a given design is laid out. There are design rules for all of the components we have been introduced to: polygons and paths, transistors, and contacts. Fundamentally, these design rules represent the physical limits of the manufacturing process.

Within a company that has the capability to manufacture integrated circuits, there is a group of people who define and optimize the manufacturing process. This “processing” group defines the design rules by trading off the cost-to-manufacture and yield, among other things, against the minimum feature size that is manufacturable by the equipment and processing steps. Other factors that influence the definition of design rules could be the maturity of the manufacturing tools and process or the market requirements for an IC or foundry service.

Overall, design rules are put in place to help layout designers understand and account for physical three-dimensional limitations and manufacturing tolerances within the CAD and layout tool environment.

Width Rule

The minimum width of a polygon (during mask-making, all paths are converted to polygons) is a critical dimension, which defines the limits of the manufacturing process (Figure 3.15). The minimum gate length of a transistor is the prime example of this rule.

A violation in a minimum width rule potentially results in an open circuit in the offending layer. The manufacturing process will not reliably produce a continuous connection or wire below a specific value, and breaks in the path would result at the point at which the width rule was violated.

In addition to single polygons, width rules can also be applied to structures such as transistors or to single polygons with electrical or other special characteristics. An example of a polygon with special electrical characteristics is a metal layer that is connected to a power supply. The larger currents that pass through these metal polygons necessitate that they have a width greater than the minimum design rule, and the correct value may depend on the size of the current rather

than being a fixed value. Large currents passing through a narrow metal track cause the track to act like a fuse, and over time or during a large current peak the metal polygon will break under the stress.

The length of a polygon (or path) is usually unlimited; however, in some processes there may be rules about minimum area requirements (for example, in the case of a contact or via where a width and a length rule together must be met). Please refer to the examples in Figure 3.15 for clarification.

Space Rule

Another critical dimension is the space rule, which is the minimum distance between two polygons. Generally, the space rule is applied to avoid an unwanted short circuit between the two polygons.

Together with the width rule on a single layer, the space and width rules define a layer pitch. The pitch of a layer is important when considering interconnect and routing porosity. The routing area consumed by n metal lines is easily calculated by multiplying the number of lines by the layer pitch. Please refer to the CD-ROM data for examples of pitch calculations.

Figure 3.16 illustrates the following points:

• 8 is an exception to example 3—the spacing rule between two polysilicon polygons may depend on their location. A typical example of this is in the case where gate polysilicon within a transistor structure has a different spacing value than that for polysilicon outside transistor structures.• 1 and 2 are examples of the metal1 to metal1 minimum space rule checked in parallel and diagonally between corners.

• 3 is an example of the poly to poly space rule where the polygons are running in parallel at a 45-degree angle.

• 4, 5, and 6 are spacing rule examples related to metal2 to metal2 spacing for polygons at a 90- and 45-degree angle.

• 7 is an example of the active to active spacing rule checked with a single distance (top example) or within a corner (bottom example).

Like the width rule, spacing rules are applied to polygons on the same layer, but also to polygons or structures on different layers or under different conditions. An example of a spacing rule on different layers is the spacing required between a contact to active and gate polysilicon. An example of a spacing rule between dif- ferent structures would be the distance between the exposed pad circuitry and sensitive internal circuitry to ensure reliable and consistent operation under all conditions.

Many of the spacing rules defined in a set of design rules can easily be under- stood when looking at a process in a cross-sectional view. This is explained fully in Section 3.5, Vertical Connection Diagram.

In Figure 3.17 we can observe that the spacing between the gate polysilicon and the contacts is not the same in the two transistors. In looking at the cross- sectional view, the first thing to note is that the source and drain areas of the two transistors are not the same.

More importantly, the spacing rule of the contact to the gate polysilicon on the left-hand transistor has been violated to the extent that the gate polysilicon has been placed directly underneath the contact. A short circuit between the metal and the gate polysilicon has been created. We can easily observe the problem in the three-dimensional view. The cross-section cut line was placed in the middle of the lower contacts.

Figure 3.17 Another example of the space rule.

Overlap Rule

As its name implies, the overlap rule is defined as the minimum overlap or surround of one polygon by another. The overlap of a metal layer over a via or contact is a prime example of this rule.

Note that this rule always involves polygons that exist on different layers, and this fact is the principal reason why this type of rule is required. Whenever structures are to be manufactured using polygons on two different layers, there is a significant chance that there will be a misalignment between the desired and actual relative placement of the two polygons. Misalignment between polygons can result in both undesired open and short circuit connections, depending on the layers involved. Fundamentally, overlap rules reduce the impact of a small misalignment between layers in the manufacturing process by ensuring that the desired connectivity is maintained.

Let’s consider an example where there is a contact between two interconnect layers. Physically, a contact polygon turns into a hole in the insulator between the two interconnect layers. The upper layer material must fill the hole and make contact with the underlying layer for the connection to be achieved.

The overlap rule states that the two layers in question must not only overlap each other; one layer must surround the other by a certain value. This value is the value for the overlap rule. In the case of the contact, the upper and lower layers must completely overlap the contact and surround the contact hole by the overlap rule value. If one of the layers does not sufficiently overlap and surround the contact hole, then the connection will not be reliable under all manufacturing conditions.

What does the overlap rule achieve? In the case where the physical polygons are not aligned perfectly, there still will be enough upper material to fill the hole. If the upper or lower layers do not completely overlap the contact hole, the area that is available for the electrical connection is reduced. This results in a poor or weak connection (unreliable!).

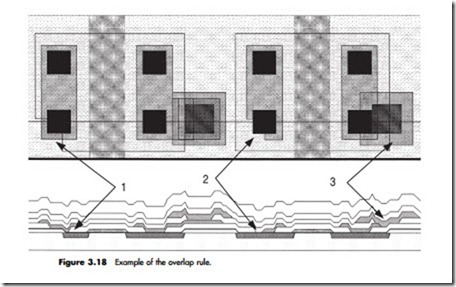

In Figure 3.18, in examples 1 and 2, observe the result of poor contacts between active and metal1. If the active is not completely overlapping the contact polygon, the contact base is not wide enough. If the metal is not completely over- lapping the contact polygon, then the contact hole is not completely filled and the contact will again result in a smaller connection surface area. In the third case we have an overlap problem between metal1 and metal2. The via has no metal1 overlap, so the connection, if any, is minimal.

The example in the figure demonstrates a case where an open circuit has a greater likelihood of happening. Let’s consider another example where a short circuit is created when an overlap rule is not obeyed.

In this case let’s consider different transistor layouts where gate polysilicon is combined with an active layer. To ensure that the transistor size is accurate and that a short circuit is avoided between the source and drain nodes, there are special rules related to transistors.

In general there are two overlap rules: active overlapping the gate and the gate overlapping the active areas. Figure 3.19 shows four different cases.

Node Out4 is an example of adequate overlap of the gate layer by the active polygon. Node Out4 is well defined. Contrast this example to node Out3. It is likely that the thin area of node Out3 will not be created.

Out1 and Out2 are examples of the gate layer overlapping the active layer. You can see that because the gate layer does not fully overlap the active area, nodes Out2 and VDD are shorted to each other, as they are part of one polygon of active.

Comments

Post a Comment