Sequential Networks:Steps for the Synthesis of Sequential Networks

Steps for the Synthesis of Sequential Networks

Let us first introduce the general model for sequential networks and then describe a sequence of steps for designing a sequential network.

General Model of Sequential Networks

A sequential network may be generally expressed in the schematic form shown in Figure 31.3. A large block represents a loopless network of logic gates only (without any flip-flops). All loops with and without flip-flops (i.e., both loops that do not contain flip-flops and loops that contain flip-flops) are drawn outside the large block.

This loopless network has external input variables x1, . . ., xn, and internal variables y1, . . ., yp, as its inputs. It also has external output variables z1, . . ., zm, and excitation variables e1, . . ., eq, as its outputs. Some of the excitation variables e1, . . ., eq are inputs to the flip-flops, serving to excite the flip-flops. The remainder of the excitation variables are starting points of the loops without flip-flops, which end up at some of the internal variables. For loops without flip-flops, ei = Yi holds for each i. For example, the network in Figure 31.2 can be redrawn in the format of Figure 31.3, placing the latches outside the loopless network.

Synthesis as a Reversal of Network Analysis

The outputs e1, . . ., eq, z1, . . ., zm of the combinational network inside the sequential network in Figure 31.3 express logic functions that have y1, . . ., yp, x1, . . ., xn as their variables. Thus, if these logic functions are given, the loopless network can be designed by the methods discussed in earlier chapters. This means that we have designed the sequential network, since the rest of the general model in Figure 31.3 is simply loops with or without flip-flops to be placed outside this combinational network. But we cannot derive these logic functions e1, . . ., eq, z1, . . ., zm directly from the given design problem, so let us find, in the following, what gap to fill in.

When loops have no flip-flops, ei = Yi holds for each i, where Y is the next value of y, and the binary- value relationship between the inputs y1, . . ., yp, x1, . . ., xn and the outputs Y1, . . ., Yq, z1, . . ., zm of the combinational network inside the sequential network in Figure 31.3 is expressed by a transition-output table. But when loops have flip-flops, we need the relationship between e1, . . ., eq, z1, . . ., zm and y1, . . ., yp, x1, . . ., xn, where e1, . . ., eq are the inputs S1, R1, S2, R2 . . . of the latches. A table that shows this relationship is called an excitation-output table. For this purpose, we need to derive the output-input relation of the S-R latch, as shown in Table 31.8, by reversing the input-output relationship in Table 31.7, which shows the output y of a latch and its next value Y for every feasible combination of the values of S and R.

In Table 31.8, d ’s mean don’t-care conditions. For example, y = Y = 0 in Table 31.8 results from S = R = 0 and also from S = 0, R = 1 in Table 31.7. Therefore, the first row in Table 31.8, y = Y = 0, S = 0, R = d, is obtained, because y = Y = 0 results from S = 0 only, but R can be 0 or 1; that is, don’t-care, d. By using Table 31.8, the transition-output table in Table 31.1, for example, is converted into the excitation- output table in Table 31.9. For example, corresponding to y1 = Y1 = 0 in the first row and the first column in Table 31.1, S1 = 0, R1 = d is obtained as the first 0d in the cell in the first row and the first column of Table 31.9, because the first row in Table 31.8 corresponds to this case. Of course, when a network, for example, Figure 31.2 is given, we can derive the excitation-output table directly from the network in Figure 31.2 rather than the transition-output table in Table 31.1 (which was derived for Figure 31.2). But when we are going to synthesize a sequential network from a transition-output table, we do not have the network yet and we need to construct an excitation-output table from a transition-output table, using Table 31.8.

Design Steps for Synthesis of Sequential Networks

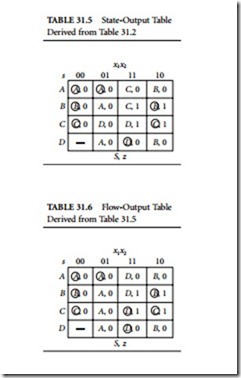

A sequential network can be designed in the sequence of steps shown in Figure 31.4. The required performance of a network to be designed for the given problem is first converted into a flow-output table. Then this table is converted into a state-output table, and next into a transition-output table, by choosing an appropriate assignment of binary numbers to all states. Then, the transition-output table is converted into an excitation-output table if the loops contain flip-flops. If the loops contain no flip-flops, the excitation-output table need not be prepared, since it is identical to the transition-output table. Finally, a network is designed, using the logic design procedures discussed in the preceding chapters.

Comments

Post a Comment