Emitter-Coupled Logic:ECL Series-Gating Circuits.

ECL Series-Gating Circuits

Figure 38.11(a) shows the basic pair of bipolar transistors in series-gating ECL, where A is connected to a power supply and B is connected to another power supply of minus voltage through a resistor. (Notice that this pair is Tx and Tr in Figure 38.2, from which Ty is eliminated.) Transistor T1 has an input x connected to its base and the other transistor T2 has a constant voltage vref at its base. As illustrated in Figure 38.2, vref is grounded through a resistor (i.e., vref = 0), where this resistor is for protection of transistor Tr from damage by a heavy current, and vref works as a reference voltage against changes of x. (The voltage at vref can be provided by a subcircuit consisting of resistors, diodes, and transistors, like the one in Figure 38.9(b).) The collector of T1 represents a logic function x because the collector of T1 can have a high voltage (i.e., logic value 1) only when T1 is non-conductive, that is, the input is a low voltage (x = 0).

The collector of T2 represents function x because it becomes a high voltage only when the input x is a high voltage (i.e., when the input is a high voltage, T1 becomes conductive and T2 becomes non- conductive because a current flows at any time through exactly one of two transistors, T1 and T2. Thus, the collector of T2 becomes a high voltage).

In Figure 38.11(b), we have two pairs of transistors. In other words, we have the pair with input y, in addition to the pair with input x shown in (a). Then let us connect them in series without Rpy , R1 and the power supply for R1, as shown in (c). The voltage at the collector of T3 is low only when T3 and T1 are both conductive and, consequently, a current i flows through T3 and T1. The voltage at the collector of T3 is high when either T3 or T1 is non-conductive (i.e., x = 0 or y = 0) and consequently no current (i.e., i) flows through T3 and T1. Thus, the collector of T3 represents the function xy, replacing the original function y shown in (b). This can be rewritten as xy = x ∨ y, so series-gating can be regarded as the OR operation.

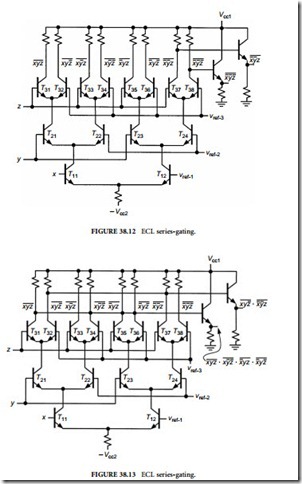

Many of the basic pair of transistors shown in Figure 38.11(a) are connected in a tree structure, as shown in Figure 38.12, where inputs x, y, and z, as well as reference voltages, vref-1, vref-2, and vref-3, need to be at appropriate voltage levels. Then the complement of all minterms can be realized at the collectors of transistors in the top level of the series connections. Two of these complemented minterms (i.e., x ∨ y ∨ z and x ∨ y ∨ z ) are shown with emitter followers, as examples at the far right end of Figure 38.12.

Some of these collectors of transistors in the top level can be collector-dotted to realize the desired logic functions, as illustrated in Figure 38.13. Notice that once collectors are collector-dotted, these collectors do not express their respective original functions.

The full adder in Figure 38.14 is a more complex example of series-gating [3]. In this figure, we use collector-dotting by tying together some of collectors to realize Wired-AND, as explained already. For example, the voltage at the collector of transistor T31 represents function xyc because of series-gating with T11, T21, and T31. Usually, at most, three transistors are connected in series (the two transistors in the bottom level, T01 and T02, in Figure 38.14 are for controlling the amount of current as part of the

power supply). This is because too many transistors in series tend to slow down the speed of the gate due to parasitic capacitances to ground. Then, by collector-dotting, some collectors of the transistors in the top level, sum s, and carry c∗ are realized, as well as their complements, s and c ∗.

Baugh and Wooley have designed a full adder in double-rail logic [2]. Ueda designed a full adder with ECL gates in single-rail logic with fewer transistors [16].

The implementation of Wired-AND in this manner requires careful consideration of readjustments of voltages and currents. (Thus, transistors or resistors may be added or changed in order to improve electronic performance, but this is not directly related to logic operations.) ECL series-gating can be extended as follows. Unlike the series-gating in Figures 38.12, 38.13, and 38.14, the same input variables are not necessarily used in each level. For example, in the top level in Figure 38.15, y and z are connected to the bases of transistors, instead of all y’s. Then, collectors can be collector-dotted, although collector-dotting is not done in this figure. Complements of products, such as xy and xz , can be realized at collectors in the top level by the series-gating, as shown in Figure 38.15. By this free connection of input variables, functions can be generally realized with fewer transistors.

CMOS has very low power consumption at low frequency but may consume more power than ECL at high speed (i.e., at high frequency). This is because the power consumption of CMOS is proportional to CFV 2, where C is parasitic capacitance, F is a switching frequency, and V is the power supply voltage. Thus, at high frequency, the power consumption of CMOS exceeds that of ECL, which is almost constant. It is important to note that compared with the standard ECL logic gate illustrated in Figure 38.1, series-gating ECL is faster with low power consumption for the following reasons:

• Because of speed-up of bipolar transistor (reduction of base thickness, and others), delay time over connections among standard ECL logic gates is greater than delay time inside logic gates and then series-gating ECL, which can realize far more complex logic functions than NOR or OR realized by standard ECL gate and consequently eliminates long connections required among standard ECL logic gates, can have shorter delay.

• A series-gating ECL circuit has lower power consumption than a logic network with standard ECL logic gates because power supplies to all standard ECL logic gates are combined into one for the series-gating ECL circuit and a current flows in only one path at any time [1,5,9,12].

• Then, in recent years, the power consumption of series-gating ECL is reduced with improved circuits [8].

• The power consumption of series-gating ECL can also be reduced by active pull-down of some emitters [14,15].

Comments

Post a Comment