Pass Transistors:Electronic Problems of Pass Transistors

Introduction

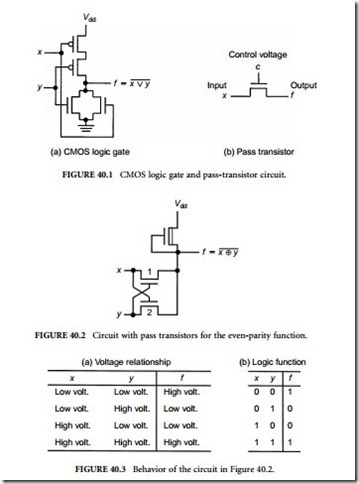

A MOSFET is usually used such that a voltage at the gate terminal of the MOSFET controls a current between its source and drain. When the voltages at the gate terminals of MOSFETs that constitute a logic gate are regarded as input variables x, y, and so on, the voltage at the output terminal represents the output function f. Here, x = 1 means a high voltage and x = 0 a low voltage. For example, MOSFETs in the logic gate in CMOS shown in Figure 40.1(a) are used in this manner and the output function f represents x ∨ y . But a MOSFET can be used such that an input variable x applied at one of source and drain of the MOSFET is delivered to the other or not, depending on whether a voltage applied at the gate terminal of the MOSFET is high or low. For example, the n-channel MOSFET shown in Figure 40.1(b) works in this manner and the MOSFET used in this manner is called a transfer gate or, more often, a pass transistor. When the control voltage c is high, the MOSFET becomes conductive and the input voltage x appears at the output terminal f (henceforth, let letters, f, x, and others represent terminals as well as voltages or signal values), no matter whether the voltage x is high or low. When the control voltage c is low, the MOSFET becomes non-conductive and the input voltage at x does not appear at the output terminal f.

Pass transistors have been used for simplification of transistor circuits. Logic functions can be realized with fewer MOSFETs than logic networks of logic gates where MOSFETs are used like those in Figure 40.1(a). The circuit in Figure 40.2, for example, realizes the even-parity function x EB y [2]. This circuit works in the following manner. When x and y are both low voltages, n-channel MOSFETs, 1 and 2, are non-conductive and consequently no current flows from the power supply Vdd to the terminal x or y. Thus, the output voltage f is high because it is the same as the power supply voltage at Vdd. When x is a low voltage and y is a high voltage, MOSFET 1 becomes conductive and 2 is non-conductive. Consequently, a current flows from the power supply to x because x is a low voltage. Thus, the output voltage at f is low. Continuing the analysis, we have the truth table shown in Figure 40.3(a). Then we can derive the truth table for function f = x EB y in Figure 40.3(b) by regarding a low and high voltages as 0 and 1, respectively. A logic gate for this function in CMOS requires 8 MOSFETs, as shown in Figure 40.4, whereas the circuit realized with pass transistors in Figure 40.2 requires only three MOSFETs. Notice that inputs x and y are connected to the sources of MOSFETs 1 and 2, unlike MOSFET in ordinary logic gates. Signal x at the source of MOSFET 1 is either sent to the drain or not, according to whether or not its MOSFET gate has a high voltage.

Pass transistors, however, are sometimes used inside an ordinary logic gate, mixed with ordinary MOSFETs. MOSFETs 1, 2, and 3 in Figure 40.5 are such pass transistors. (Actually, the pair of 1 and 2 is a transmission gate to be described in the following and also in Chapter 39, Section 39.2) Logic networks in CMOS where MOSFETs are used in the same way as those in Figure 40.1(a) can sometimes be simplified by an appropriate use of pass transistors, possibly with speed-up.

The wide use of a pass transistor is found in the DRAM memory cell, which consists of one capacitor and one pass transistor. The control of charging to or discharging from the memory capacitor is done through the pass transistor. This shows the impact of this technique in area reduction, power consumption reduction, and possibly also in speed-up. Pass transistors are also used in the arithmetic-logic unit of a computer, which requires speed and small area, such as fast adders (actually the logic gate in Figure 40.5 is part of such an adder), multipliers and multiplexers [3,7,11,12].

The circuit in Figure 40.6(a) in double-rail input logic (i.e., x, x, y, and y are available as inputs)

realizes the odd-parity function x EB y . A circuit for the inverter shown by the triangle with a circle in Figure 40.6(a) is shown in (b).

Pass transistors are often used for forming a demultiplexer, as illustrated in Figure 40.7. Series connection of pass transistors has some resistance. So the number of control variables (here, x and y) is limited to at most four and the inverter shown in Figure 40.6(b) is added after input g as a buffer.

Using pass transistors, a latch (more precisely speaking, a D latch to store data) can be constructed as shown in Figure 40.8. When control input c is a high positive voltage, the feedback loop is cut by the pass transistor with c , and the input value is fed into the cascade of two inverters. When c becomes a low voltage, the input is cut off and the loop that consists of two inverters and one pass transistor retains the information. The use of pass transistors in logic networks, however, has been very limited because of electronics problems to be discussed in the following. The majority of commercially available logic networks have been in static CMOS circuits. But as higher speed and smaller area are desired, this situation is gradually changing. The pass-transistor logic has recently attracted much attention under these circumstances and is anticipated to be widely used in the near future for its area/power saving and high-performance benefits. Beside pass transistors, there are many other unconventional MOS networks. All these networks are useful for simplification of electronic realization of logic networks or for improvement of performance, although complex adjustments of voltages or currents are often required.

Electronic Problems of Pass Transistors

Suppose an n-channel MOSFET is used as a pass transistor, as shown in Figure 40.9. Then, the MOSFET behaves electronically as follows. When the control voltage at c is high, the voltage at the input x is delivered to the output terminal f, no matter whether the voltage at the input x is high or low. But if the voltage at the input x is high, a current flows through the MOSFET to charge up the parasitic capacitance (shown in the dotted lines in Figure 40.9) at f and stops when the difference between the voltage at f and the voltage at c reaches the threshold voltage, making the voltage at f somewhat lower than the voltage at x. When the voltage at c becomes low, the pass transistor becomes non-conductive and the electric charge stored on the parasitic capacitance gradually leaks to the ground through the parasitic resistor.

If the voltage at the input x is low when the control voltage at c is high, the electric charge stored on the parasitic capacitance flows to the ground through the pass transistor and input terminal x also if it has not completely leaked to the ground yet.

This complex electronic behavior of the pass transistor makes a circuit with pass transistors unreliable. The intermediate value of the voltage at f, which is lower by the threshold voltage than the voltage at x or partially leaked voltage, causes unpredictable operations of the logic network when the voltage at f is fed to ordinary CMOS logic gates in the next stage. Moreover, it degrades the switching speed of the CMOS logic gates. In the worst case, the circuit loses noise margin or it does not operate properly.

There are three techniques to avoid this drawback. The first one is to combine an nMOS pass transistor and a pMOS pass transistor in parallel, as shown in Figure 40.10(a). With this technique, when the pass transistor is conductive, the output voltage at f reaches exactly the same value as the input voltage at x, no matter whether the input voltage is high or low. This pair of nMOS and pMOS pass transistors is sometimes called a transmission gate. Although this has better stability over the pass transistor circuit in Figure 40.9, it consumes roughly twice as large an area.

The second approach is to use a pMOS feedback circuit at the output of the nMOS pass transistor, as shown in Figure 40.10(b). The gate of a p-channel MOSFET is driven by the CMOS inverter (shown as the triangle with a small circle), which works as an amplifier. When the CMOS inverter discharges the electric charge at the output, it also turns on the feedback pMOS to raise the pass transistor output to the power supply voltage, eliminating the unreliable operation. One limitation of this approach is that it does not solve the degradation of switching speed due to low voltage, because the speed is determined by the initial voltage swing before the pMOS turns on. Area increase with this approach is smaller than the transmission gate in Figure 40.10(a).

The third approach is to raise the gate voltage swing up to the normal voltage plus threshold voltage, which is used in DRAM and referred to as “word boost,” as shown in Figure 40.10(c). This approach requires a boost driver every time the gate signal is generated, which is difficult to use in logic functions in general. In addition, a voltage that is higher than the power supply voltage is applied to the gate of a MOSFET, which requires special care against breakdown and reliability problems (these need to be solved by increasing the thickness of gate insulation).

Another important consideration for pass-transistor operation is how many pass transistors can be connected in series without buffers. Many pass transistors connected in series can be treated as a serially connected resistor-capacitor circuit. The delay of this RC (resistor-capacitor) circuit, which is proportional to the product of R and C, becomes roughly four times larger when both R and C are doubled. Thus, the delay of this circuit is proportional to the square of the number of pass transistors. This means that it is not beneficial to increase the number of pass transistors too many. However, short-pitch insertion of CMOS inverters increases the delay overhead of the buffers themselves. Empirically, the optimal pass-transistor stages for delay minimization is known to be about two to three. In design practice, the number of pass transistors cannot be arbitrarily chosen because designers want to have a certain number of fan-out connections and a buffer cannot support too many fan-outs and pass transistors. Also, the structure of a logic network cannot be arbitrarily chosen because of area size and power consumption.

Comments

Post a Comment