Adders:Serial Adder

Serial Adder

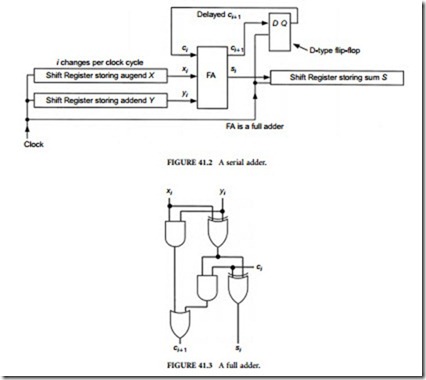

A serial adder operates similarly to manual addition. The serial adder, at each step, calculates the sum and carry at one bit position. It starts at the least significant bit position (i.e., i = 0) and each successive next step it sequentially moves to the next more significant bit position where it calculates the sum and carry. At the n-th step, it calculates the sum and carry at the most significant bit position (i.e., i = n – 1). In other words, the serial adder serially adds augend X and addend Y by adding xi, yi, and ci at the i-th bit position from i = 0 to n – 1. From the truth table shown in Table 41.1, we have sum bit si = xi ⊕ yi ⊕ ci and carry to the next higher bit position ci+1 = xi ·yi ∨ ci ·(xi ∨ yi) (also ci+1 = xi · yi ∨ ci · (xi ⊕ yi)), where “·” is AND, “∨” is OR, and “⊕” is XOR, and henceforth, “·” will be omitted. This serial addition can be realized by the logic network, called a serial adder, or bit-serial adder, shown in Figure 41.2, where its operation is synchronized by a clock. The addition of each i-th bit is done at a rate of one bit per cycle of clock, producing sum bits, si’s, at the same rate, from the least significant bit to the most significant one. In each cycle, si and ci+1, are calculated from xi, yi, and the carry from the previous cycle, ci. The core logic network, shown in the rectangle in Figure 41.2, for this one-bit addition for the i-th bit position is called

a full adder (abbreviated as FA). We obtain a logic network for an FA shown in Figure 41.3 using AND, OR, and XOR gates. A D-type flip-flop may be used as a delay element which stores the carry for a cycle. Full adders realized in ECL (emitter-coupled logic) are described in Chapter 38. FAs with a minimum number of logic gates are known for different types of logic gates [10].

A serial subtracter can be constructed with a minor modification of a serial adder, as explained in the last paragraph of Section 41.2.

Comments

Post a Comment