MOS Field-Effect Transistors (MOSFETs)part1

MOS Field-Effect Transistors (MOSFETs)

UNIT 1 OUTLINE

1.1 Device Structure and Physical Operation

1.2 Current – Voltage Characteristics

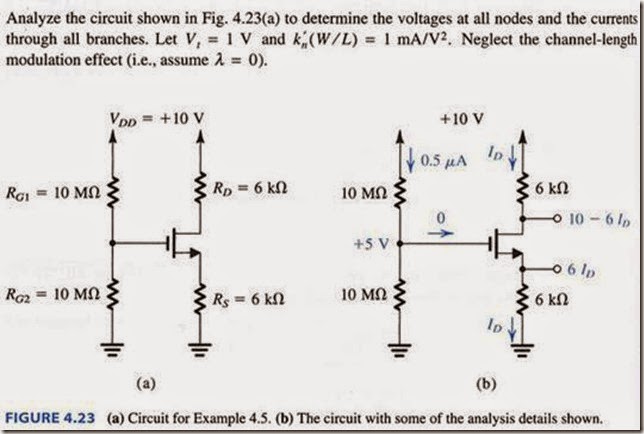

1.3 MOSFET Circuits at DC

1.4 Biasing in MOS amplifier circuits

1.5 Small Signal Operation and Models

1.6 The MOSFET as an Amplifier and as a Switch

1.7 Single Stage MOS amplifiers

1.8 SPICE MOSFET models and examples

LEARNING OUTCOMES:

At the end of this chapter one can clearly get to know the following:

· Understanding Physical construction and operation of an Enhancement MOSFET

· Drawing the V-I characteristics of n and p channel E-MOSFET

· DC operation or biasing of MOSFETs

· AC Operation: Small signal modeling of MOSFETs

· Single stage MOS amplifiers : Common Source, Common Drain and Common Gate amplifiers

· SPICE modeling of MOSFETs INTRODUCTION

Along with the Junction Field Effect Transistor (JFET), there is another type of Field Effect Transistor available whose Gate input is electrically insulated from the main current carrying channel and is therefore called an Insulated Gate Field Effect Transistor or IGFET. The most common type of insulated gate FET which is used in many different types of electronic circuits is called the Metal Oxide Semiconductor Field Effect Transistor or MOSFET for short.

The IGFET or MOSFET is a voltage controlled field effect transistor that differs from a JFET in that it has a "Metal Oxide" Gate electrode which is electrically insulated from the main semiconductor N-channel or P-channel by a thin layer of insulating material usually silicon dioxide (commonly known as glass). This insulated metal gate electrode can be thought of as one plate of a capacitor. The isolation of the controlling Gate makes the input resistance of the MOSFET extremely high in the Mega-ohms (MΩ) region thereby making it almost infinite.

As the Gate terminal is isolated from the main current carrying channel "NO current flows into the gate" and just like the JFET, the MOSFET also acts like a voltage controlled resistor were the current flowing through the main channel between the Drain and Source is proportional to the input voltage. Also like the JFET, this very high input resistance can easily accumulate large amounts of static charge resulting in the MOSFET becoming easily damaged unless carefully handled or protected.

MOSFETs are three terminal devices with a Gate, Drain and Source and both P-channel (PMOS) and N-channel (NMOS) MOSFETs are available. The main difference this time is that MOSFETs are available in two basic forms:

1. Depletion Type - the transistor requires the Gate-Source voltage, (VGS) to switch the device "OFF". The depletion mode MOSFET is equivalent to a "Normally Closed" switch.

2. Enhancement Type - the transistor requires a Gate-Source voltage, (VGS) to switch the device "ON". The enhancement mode MOSFET is equivalent to a "Normally Open" switch.

Basic operating principle of a MOSFET:

· Use of the voltage between two terminals to control the current flowing in the third terminal

· Also, the control signal can be used to cause the current in the third terminal to change from zero to a large value, thus allowing the device to act as a

switch.

The FET differs from BJT in the following important characteristics:

1. It is a unipolar device

2. It is simpler to fabricate

3. Occupies less space in Integrated form, packaging density is high(>200 million)

4. It has higher input resistance

5. It can be used as a symmetrical Bilateral switch

6. It functions as a memory device

7. It is less noisy than a BJT

8. It exhibits no offset voltage at zero input, hence making an excellent signal chopper

THE ONLY DISADVANTAGE IS IT HAS SMALLER GAIN- BANDWIDTH PRODUCT THAN BJT

The symbols and basic construction for both configurations of MOSFETs are shown below.

DEVICE STRUCTURE AND PHYSICAL OPERATION

Device Structure:

Figure 4.1 shows the physical structure of the n-channel enhancement-type MOSFET. The transistor is fabricated on a p-type substrate. Two heavily doped n-type regions: the n+ source and the n+ drain regions, are created in the substrate.

1. A thin layer of silicon dioxide (SiO2) of thickness tox (typically 2-50 nm) - an excellent electrical insulator, is grown on the surface of the substrate, in the area between the source and drain regions.

2. Metal is deposited on top of the oxide layer to form the gate electrode.

3. Metal contacts are also made to the source region, the drain region, and the substrate,

also known as the body.

Thus four terminals are brought out: the gate terminal (G), the source terminal (S), the drain terminal (D), and the substrate or body terminal (B).

A voltage applied to the gate of the MOSFET controls current flow between source and drain. This current will flow in the longitudinal direction from drain to source in the region labelled “channel region.”

This region has a length L in the range of 0.1 µm to 3 µm, and a width W in the range of 0.2 µm to 100 µm.

Note: The MOSFET is a symmetrical device [its source and drain can be interchanged with no change in device characteristics].

(i) With No Gate Voltage

With no bias voltage applied to the gate, two back-to-back diodes exist in series between drain and source. They prevent current conduction from drain to source when a voltage VDS is applied. The path between drain and source has a very high resistance (of the order of 1012Ω).

(ii) Creating a Channel for Current Flow

The source and the drain are grounded and a positive voltage is applied to the gate.

The positive voltage on the gate causes the free holes (which are positive charged) to be repelled from the region of the substrate under the gate. These holes are pushed downward into the substrate, leaving behind a carrier-depletion region as shown below.

The positive gate voltage attracts electrons from the n+ source and drain regions into the channel region. When a sufficient number of electrons accumulate near the surface of the substrate under the gate, an n region is in effect created, connecting the source and drain regions, as indicated in Fig. 4.2. This MOSFET is called an n-channel MOSFET or, alternatively, an NMOS transistor. The induced channel is also called an inversion layer. The induced n region thus forms a channel for current flow from drain to source.

Note: The value of VGS at which a sufficient number of mobile electrons accumulate in the channel region to form a conducting channel is called the threshold voltage and is denoted Vt.

The value of Vt is controlled during device fabrication and typically lies in the range of

0.5 V to 1.0V.

Now if a voltage is applied between drain and source, current flows through this induced n region.

The gate and the channel region of the MOSFET form a parallel-plate capacitor, with the oxide layer acting as the capacitor dielectric. An electric field thus develops in the vertical direction. It is this field that controls the amount of charge in the channel, and thus it determines the channel conductivity and, in turn, the current that will flow through the channel when a voltage vDS is applied.

(iii) Effect of Applying a Small VDS

We now apply a small positive voltage VDS between drain and source, as shown in Fig. 4.3.

• The voltage vDS causes a current iD to flow through the induced n channel. Current is carried by free electrons traveling from source to drain.

• The magnitude of iD depends on the density of electrons in the channel, which in turn depends on the magnitude of vDS

• Specifically, for vGS= Vt, more electrons are attracted into the channel.

• The result is a channel of increased conductance or, equivalently, reduced

resistance. In fact, the conductance of the channel is proportional to the excess gate voltage(vGS-Vt), also known as the effective voltage or the overdrive voltage.

• Figure 4.4 shows a sketch of iD versus vDS for various values of vGS. We observe that the MOSFET is operating as a linear resistance whose value is controlled by vGS.

• The resistance is infinite for vGS≦Vt, and its value decreases as vGS exceeds Vt.

• Specifically, the channel conductance is proportional to vGS–Vt, and thus iD is

proportional to (vGS–Vt) vDS.

• Then, increasing vGS above the threshold voltage Vt enhances the channel, hence the name enhancement-mode operation and enhancement-type MOSFET. Finally, we

note that the current that leaves the source terminal (iS) is equal to the current that enters the drain terminal (iD), and the gate current iG= 0.

The expression for the channel resistance can be determined as follows:

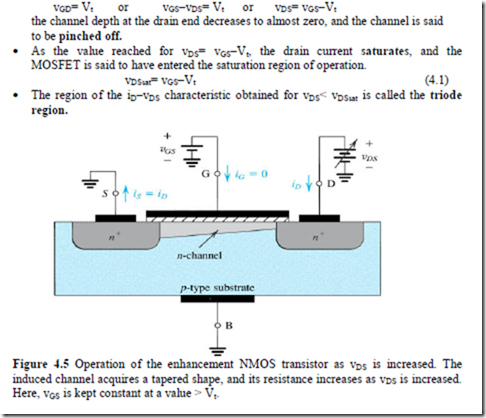

(iv) Operation as vDS Is Increased

• As we travel along the channel from source to drain, the voltage (measured relative to the source) increases from 0 to vDS.

• Thus the voltage between the gate and points along the channel decreases from

vGS at the source end to vGS–vDS at the drain end.

• Since the channel depth depends on this voltage, we find that the channel is no longer of uniform depth. As vDS is increased, the channel becomes more tapered and its resistance increases correspondingly.

· When vDS is increased to the value that reduces the voltage between gate and channel at the drain end to Vt ,

Derivation of the iD-vDS Relationship

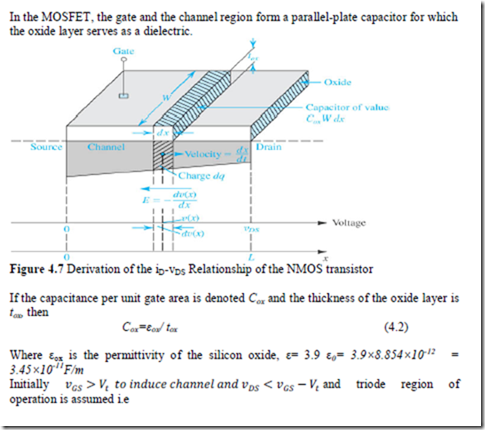

In the MOSFET, the gate and the channel region form a parallel-plate capacitor for which the oxide layer serves as a dielectric.

The gate and channel region form a parallel plate capacitor with oxide layer as the dielectric. If the capacitance per unit area is Cox and the thickness of the oxide layer is tox Now consider the infinitesimal strip of the gate at distance x from the source.

To find the charge stored on this strip of gate capacitance, we multiply capacitance by effective voltage between Gate and the Channel at point x

The voltage vDS produces an electric field along the channel in the negative x direction.

At point x this field can be expressed as

The Electric field E(x) causes the electron charge dq to drift toward the drain with a velocity dx/dt

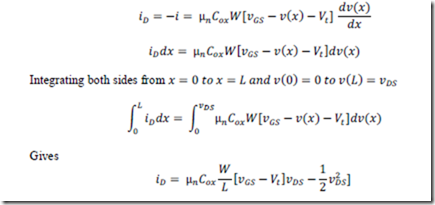

The resulting drift current ‘i’ can be obtained as follows:

Substituting the above values, the drain current ‘i’ can be obtained as follows:

Since the current ‘i’ is constant at all points along the channel it must be equated to the drain current iD

In the saturation region substituting we get

The process transconductance parameter is denoted kn’ and kn’=µnCox Therefore the iD –vDS relationship can be expressed in terms of kn as follows:

• The drain current is proportional to the ratio of the channel width W to the channel length L, known as the aspect ratio of the MOSFET.

• For a given fabrication process, however, there is a minimum channel length, Lmin.

In fact, the minimum channel length that is possible with a given fabrication process is used to characterize the process and is being continually reduced as technology advances. State of the art MOS technology is a 0.13-µm process, meaning that for this process the minimum channel length possible is 0.13 µm, corresponding to a minimum width of 0.16 µm and tox= 2nm.

Solution:

4.1.7 The p-Channel MOSFET

A p-channel enhancement-type MOSFET (PMOS transistor), fabricated on an n-type substrate with p+ regions for the drain and source, has holes as charge carriers.

The device operates in the same manner as the n-channel device except that vGS and vDS are negative and the threshold voltage Vt is negative. Also, the current iD enters the source terminal and leaves through the drain terminal.

In general, NMOS devices are normally preferred to PMOS because

- Smaller

- Operate faster and

- Requires lower supply voltages than PMOS.

4.1.8 Complementary MOS or CMOS

As the name implies, complementary MOS technology employs MOS transistors of both polarities. At present time CMOS is the most widely used of all the IC technologies. Figure 4.9 shows cross-section of a CMOS chip illustrating how the PMOS and NMOS transistors are fabricated. While the NMOS transistor is implemented directly in the p- type substrate, the PMOS transistor is fabricated in a specially created n region, known as an nwell.

4.2 CURRENT-VOLTAGE CHARACTERISTICS of an n-channel E-MOSFET

The drain is always positive relative to the source in an n-channel FET. The circuit Symbol for an n-channel E-MOSFET is as shown below:

figure 4.10 (a) Circuit symbol for the n-channel enhancement-type MOSFET.

(b) Modified circuit symbol with an arrowhead on the source terminal to distinguish it from the drain and to indicate device polarity (i.e., n channel). (c) Simplified circuit symbol to be used when the source is connected to the body or when the effect of the body on device operation is unimportant.

Consider an n-channel enhancement-type MOSFET with voltages vGS and vDS applied and with the normal directions of current flow indicated.

There are three distinct regions of operation: the cutoff region, the triode region, and the saturation region.

• The saturation region is used if the FET is to operate as an amplifier.

• For operation as a switch, the cutoff and triode regions are utilized

To operate the MOSFET in the triode region we must first induce a channel,

And then keep vDS small enough so that the channel remains continuous. This is achieved by ensuring that the gate-to-drain voltage is

The n-channel enhancement-type MOSFET operates in the triode region when vGS is greater than Vt and the drain voltage is lower than the gate voltage by at least Vt volts.

In the triode region, the iD-vDS characteristics can be described by

where kn’= µnCox is the process transconductance parameter. If vDS is sufficiently small

The boundary between the triode region and the saturation region is characterized by

Substituting this value of vDS into Eq. (4.11)

Since the drain current is independent of the drain voltage, the saturated MOSFET behaves as an ideal current source whose value is controlled by vGS according to the nonlinear relationship in the above Eq.

Finite Output Resistance in Saturation

Change in vDS in saturation, implies no change in corresponding iD and hence infinite resistance in saturation. This is because of the assumption that once channel is pinched off, further increase in vDS have no effect on the channel’s shape. But, in practice, as vDS is increased, the channel pinch-off point is moved slightly away from the drain, toward the source.

Channel Length Modulation: With an increase in vDS, the channel length decreases from L to L-ΔL, but voltage drop across it remains the same, and the additional drop will appear across the depletion region between the end of the channel and the drain

The extrapolated characteristics intersect the x-axis at VA, and the corresponding value of vDS for iD=0, from the equation will be -1/ λ

VA = 1/ λ and VA = VA’L V/µm where VA is called Early Voltage

With the dependence of iD on vDS, we can now define the output resistance as follows:

4.2.4 Characteristics of the p-Channel MOSFET

The circuit symbol for the p-channel enhancement-type MOSFET is shown in Fig. 4.18(a). Recall that for the p-channel device the threshold voltage Vt is negative. To induce a channel we apply a gate voltage that is more negative than Vt.

And apply a drain voltage that is more negative than the source voltage.

· To operate in the triode region VDS must satisfy

The symbols and Circuit diagram to measure V-I characteristics of a p-channel MOSFET are as shown below:

Comparison of NMOS and PMOS FETs

The NMOS and PMOS FETs are compared in terms of their symbol representation and large signal equivalent models as shown below:

4.2.5 The Role of the Substrate---The body Effect

In most of the applications the Source and Body terminals are connected and therefore VSB =0 and it has no effect on the circuit operation. But, in IC’s, substrate is connected to the most negative voltage, making SB junction reverse biased, hence the depletion region around the channel increases decreasing the channel depth

This decrease in channel depth should be compensated by a corresponding increase in Vt

The body voltage controls iD; thus the body acts as another gate for the MOSFET, a phenomenon known as the body effect. Here we note that the parameter γ is known as the body-effect parameter

4.2.6 Temperature Effects

1. The magnitude of Vt decreases by about 2 mV for every 1oC rise in temperature.

This decrease in |Vt| gives rise to a corresponding increase in drain current as temperature is increased.

2. But, K’ decreases with temperature and its effect is dominant.

Therefore, Overall effect is decrease in iD with increase in temperature

4.2.7 Breakdown and Input Protection

There are three types of Breakdown:

· Weak avalanche: For VDS>20V up to 150V avalanche breakdown between D and Substrate causing large drain currents

· Punch through: Occurs in short channel devices for smaller voltages, when depletion region of drain extends to source, through the channel

· Permanent breakdown: Due to high values of VGS in the range of 30V which may cause the thin oxide layer to be ruptured. Therefore Input protection circuits are provided with MOSFETs

MOSFET CIRCUITS AT DC - Examples

Problem 1:

Problem 2

Figure 4.26(b) shows a sketch of MOSFET’s iD-vDS characteristic curves superimposed on which is a straight line representing the iD-vDS relationship of Eq.(4.37). The straight line in Fig.4.26(b) is known as the load line.

· For any given value of vI<Vt, the transistor will be cut off, as shown in the iD-vDS curve and find vo from the point of intersection of this curve with the load line.

· The circuit works as follows: Since vGS=vI, we see that for vI<Vt, the transistor will be cut off, iD will be zero, and vo=vGS=VDD. Operation will be at the point labeled A.

· As vI exceeds Vt, the transistor turns on, iD increases, and vo decreases. Since vo will initially be high, the transistor will be operating in the saturation region. This corresponds to points along the segment of the load line from A to B.

• The switch is turned on by applying a voltage close to VDD, resulting in operation close to point C with vo very small (at C, vo=Voc).

The common-source MOS circuit can be used as a logic inverter with the “low” voltage level close to 0 V and the “high” level close to VDD.

4.4.4 Operation as a Linear Amplifier

• To operate the MOSFET as an amplifier we make use of the saturation-mode segment of the transfer curve.

• The device is biased at a point located somewhere close to the middle of the curve; point Q called the quiescent point.

• The voltage signal to be amplified vi is then superimposed on the dc voltage VIQ as shown in Fig.4.26(c).It can be seen that the amplifier will be very linear, and vo will have the same waveform as vi except that it will be larger by a factor equal to the voltage gain of the amplifier at Q

• The voltage gain is equal to the slope of the transfer curve at the bias point Q.

• Observe that the slope is negative, and thus the basic CS amplifier is inverting.

4.4.5 Analytical Expressions for the Transfer Characteristic

The i-v relationships that describe the MOSFET operation in the three regions- cutoff, saturation, and triode- can be easily used to derive analytical expressions for the three segments of the transfer characteristics.

Therefore, the expression for the incremental voltage gains Av at a bias point Q at which VI = VIQ as follows:

4.5 BIASING IN MOS AMPLIFIER CIRCUITS

· An essential step in the design of a MOSFET amplifier circuit is the establishment of an appropriate dc operating point for the transistor.

· This is the step known as biasing or bias design

4.5.1 Biasing by Fixing VGS

The most straightforward approach to biasing a MOSFET is to fix its gate-to-source voltage VGS to the value required to provide the desired ID.

Biasing by fixing VGS is not a good technique.

1. Vt, Cox and W/L vary widely among devices

2. Vt and µn depend on temperature

4.5.2 Biasing by Fixing VG and Connecting a Resistance in the Source

An excellent biasing technique for discrete MOSFET circuits consists of fixing the dc voltage at the gate, VG, and connecting a resistance in the source lead, as shown in Fig.4.30 (a). For this circuit we

Resistor Rs provides negative feedback, which acts to stabilize the value of the bias current ID. This gives it the name degeneration resistance

Figure 4.30(b) provides a graphical illustration of the effectiveness of this biasing scheme. The intersection of this straight line with the iD-VGS characteristic curve provides the coordinates (ID and VGS) of the bias point. Observe that compared to the case of fixed VGS, here the variability obtained in ID is much smaller.

Two possible practical discrete implementations of this bias scheme are shown in Fig.4.30(c) and (e).

4.19 Repeat Example 4.9 when fixed VGS bias is used. The circuit for fixed VGS bias is as shown below:

Let the drop across the drain resistor RD and the drain source voltage of MOSFET VDS be equal = 15/2=7.5V

4.5.3 Biasing Using a Drain-to-Gate Feedback Resistor

Here the large feedback resistance RG (usually in the MΩ range) forces the dc voltage at the gate to be equal to that at the drain (because IG=0) as shown in figure Fig. 4.32. Thus we can write

4.5.4 Biasing Using a Constant-Current Source

The most effective scheme for biasing a MOSFET amplifier is that using a constant- current source. Figure 4.33(a) shows such an arrangement applied to a discrete MOSFET. A circuit for implementing the constant-current source I is shown in Fig. 4.33(b).

Comments

Post a Comment